This one started when my 50-year old (!) Minimoog bit the big one.

Its Loudness Contour Envelope Generator croaked; it would work on occasion if I tapped on the DECAY TIME knob--so, a faulty potentiometer?

I took it to an expensive vintage electronics repair shop 45+ minutes away.

Sadly, $600USD later, after "fixing" it, the sustain knobs sent CV to the VCA and VCF, even if a key wasn't depressed. Need to do a soundcheck? Have the roadie crank up "Sustain Level". Done.

Not a feature, a bug?

|

| MiniMoog "Modifiers" section. On my vintage Mini this is transistor/resistor/cap/diode only ADSD Envelope Generator. |

If so, I needed to understand how the Mini's EG worked.

Looking at MiniMoog schematics (here and here), its EG's are discrete; no IC's.

I had (and still have) almost no experience with circuit design from this era: pre-integrated circuit, but post-vacuum tubes.

The more I tried to study the schematics and follow signal paths the more my brain hurt.

I tried to simulate the MiniMoog's Loudness EG using Falstad:

|

| Get a functional (pun intended) MiniMoog Loudness Contour simulation here. I couldn't get this Falstad simulation to work, but Mod Wiggler's "guest"--the same superhero who helped save the triangle to ramp design in the DVCO project, here--fixed my broken Moog EG sim. Yeh! |

Cool...I had a working simulation, but try as I might, I could not duplicate the odd "Sustain to CV" fault on my beloved MiniMoog.

So--I did what any rational person would do--I gave up.

Of course, I couldn't leave it alone.

Instead, I went down a design using only discrete rabbit hole.

Nevertheless, I dug further into Falstad to (try to) whip up discrete simulations for LFO's, preamps, and EG's.

I quickly learned that, like my brain, the UI for Falstad wasn't up to some of it.

Which led me to--sorry about the long intro, folks--the NGSPICE simulation abilities built into our beloved EDA software--KICAD 8. Simulating discrete component circuits for me was way easier than endless breadboarding.

TUTORIALS

To simulate circuits, Kicad (an open source project) incorporates code from another open source project, NGSPICE; NGSPICE'S beginner's tutorial page is

here but the how-to doesn't help much for Kicad.

To learn Kicad 8's NGSPICE user interface: watch at least some of the 7-part video series starting

here.

This is essential viewing. The content creator presents his tutorials slowly; he's thorough, easy to follow, and accurate--worth the time.

GETTING STARTED--FAKE DC POWER

Something that puzzled me--how could I "turn on" a simulation?" There is no breadboard to wire anything to, no PCB to fry with a bench supply.

To provide fake power to a fake circuit: in a Kicad 8 schematic, I placed a component called SPICE > VDC:

|

| Spice VDC component |

I added the usual +5V power pin and GND to this VDC spice supply.

I edited its properties, renamed it V1, and gave it a 5 volt DC voltage; when my simulation power was ready to go it looked like this:

|

| Once +5VDC was defined somewhere in my schematic, I found I couldn't define a Spice VDC for +5V again or cryptic errors would appear when it came time to simulate the circuit. |

| |

To create a phony bipolar supply I could craft something like this:

|

Simulated +/- 15V Power supply

|

With this in place, I could use +5, +15, GND and so on, "powering up" my circuit during simulation.

Moving on:

555 ASTABLE: FIRST SIMULATION

Back when dinosaurs roamed the earth I built an astable using the venerable 555 IC. As an homage, for my first simulation using Kicad, I started there.

|

| 555-the newbie's IC! |

But! Putting a 555 symbol, passive components, and my +5VDC power supply into a Kicad schematic, then starting the simulation (steps to start a simulation follow shortly), threw cryptic errors.

Turned out: the simulation didn't know what to do with a 555 IC, since its behavior needed to be defined or "modeled".

I found models for just about every component I could think of using Google searches--often they are found on manufactures' websites. I gathered a few model files I thought I'd use frequently and put them on Github--here.

Here's a quick summary of how to add a model to a Kicad symbol:

- Select the 555 symbol in the schematic

- Tap "e" key to select properties

- Click on the "Simulation Model" button:

- Point the component to the 555 simulation file and choose the 555 model:

Click on the PIN assignments tab to make sure the pins from the model map to the pins in the Kicad symbol:

With this in place--was I good to go?

I started the simulation using Inspect > Simulator

I created a new simulation using the "plus" icon:

I chose: "OP - DC Operating Point". OP was akin to using a voltmeter, so I figured--easy?

....and to my surprise it showed voltages and current for a sim as a snapshot in time: IT WORKED!!!

Cool!!!!!

SCOPE A DOPE

Seeing voltages and currents at a point in time was great, but I wanted to take it up a notch: see an X as time and Y as amplitude.

I put the 555 astable schematic into a hierarchical sheet (a brief how-to covering Kicad hierarchical sheets is here--go to the bottom of the post).

Using this 555 astable to generate a couple of pulses in 30 seconds I crafted a three transistor attack/release envelope generator:

To edit an existing simulation, I used this icon:

|

| TRAN--something the GOP will outlaw before long? No, blogs like this go first. |

I chose, as my type of simulation, "TRANS", an abbreviation for "Transient Analysis", the simulation akin to capturing the output of an oscilloscope.

"Time step" formed the sample rate, "final time" constituted how many seconds of data my fake scope's Y axis showed:

|

| I found that making time steps too big or too small could bring the simulation to its knees. For this simple A/R function generator, plotting every 10ms and doing so for 30 seconds did the trick. |

With the simulation successfully launched: to choose the voltage I wanted to see plotted over time, on the right column I chose "V(OUT)", indicating the label I added to the AR schematic seen above.

I ran it and it worked! The V(OUT) looked pretty good--attack and release resistance impacted the circuit's peak output voltage but for 3 transistors: good enough.

|

| I also needed to get a 2N7000 simulation model for this as well. I found it here--again, a manufacturer's website is a good place to start your model file journey. |

DIGITAL SIMULATION

With my pseudo-analog AR design working I was on a roll--could Kicad be used for digital simulations?

Specifically: some older ADSR's have SR latches (the "discrete ADSR"

here for instance), could I get an 74LS00 simulation to work?

Once again the tutorials

here and

here made this pretty easy; I got the models for some of the 74HCxx IC family

here--downloaded from the link next to "models for 74xx digital devices, a NGspice subset derived from the MicroCap library."

Setting up the simulation was not too difficult, but I found I couldn't skip a step and have it work--these tips are in the aforementioned videos, but, here they are again:

- I tied outputs I wanted to see in my simulation to an 1M resistor, which is in turn tied to GND. Otherwise, the simulation wouldn't work.

- I made sure I added this text to the simulation's .kicad_sch design (this assumed "5V = high" logic):

|

| I have no idea why this is needed....just do it. |

- I didn't need to worry about the power pins on a simulated digital IC, at least for the 74xx series mentioned in the video.

- Since I was doing a transient analysis of a digital simulation, I unchecked "Save all Currents" and "Save all power dissipations" and selected "PSpice and LTSpice" as my "compatibility mode" (you knew this, right?). Otherwise the simulations throws cryptic error and warning messages and may not run.

With all of that--and it all had to be right for any of it to work--I got a 7400 simulation going:

|

Notice that no power section "E" is needed.

|

|

| Output. |

OTA's

I simulated those too....took me a day to figure out I needed to use the VSIN (voltage) spice part, not the ISIN (current) part. Doh! That simple mistake tripped me up for hours.

Again, you can get the model files I have tested working with Kicad/NGSPICE here.

|

| 13700...Could only find a model for 1/2 the IC. The "1/2 LM13700" symbol is available as in the library file found here. |

|

| CA3080 |

|

| Seems worked: green is input sine, output is amplified signal (I got the 13700's built-in Darlington buffer to work, and also an op amp based buffer) |

PLOTTING FREQUENCY RESPONSE

To wrap it up I drew a simple schematic, in this case an RC filter:

I used a 2 pin connector for the input, not a spice component.

Clicked on J1, clicked E for properties then chose the Simulation Model button:

Under settings--I selected "built in SPICE model"'; Device Type: DC and AC magnitude Value 1; DC value 0:

For the simulation I set up "AC small signal analysis" with these values (stop frequency for audio should be anywhere from perhaps 10Hz to 100K)

When I simulated the filter I got a nice roll off plot:

Good for trying what-if's, dropping in different cap and resistor values--seeing what happens--why do math, ever?

Good video that goes over AC Small Signal Analysis in Kicad 8 is

here.

THIS BLOG'S SPONSOR!

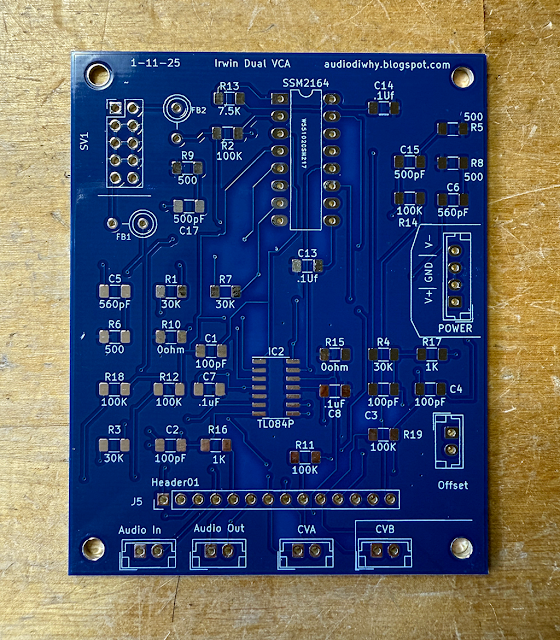

Before I go, got to shout it out for this blog's sponsor, PCBWAY. Once you have your simulation working, it's not hard to turn it into a real .sch/.pcb and gerber file and send it off to PCBWAY. They will get it back to you super fast....PCBWAY fabricates at incredibly low prices (5x 2 layer boards for about $5 US.....). Hats off to them, I am grateful for their sponsorship of this blog.

ABRUPT TAPE SPLICE

That's it for this time, paraphrasing the great

Quintus Arrius: "you have the spirit to watch

bad YouTube, but the good sense to control it". Simulate well and live! See ya next time.